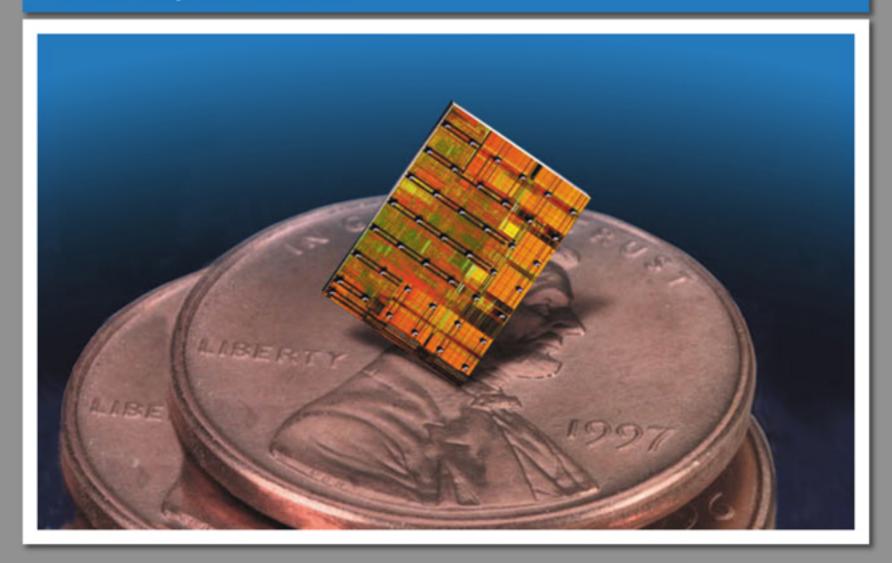

#### **Current Applications of Integrated Circuits ("Chips")**

# Today, Chips Must Contain Millions of Components, Yet Be Very Small in Size

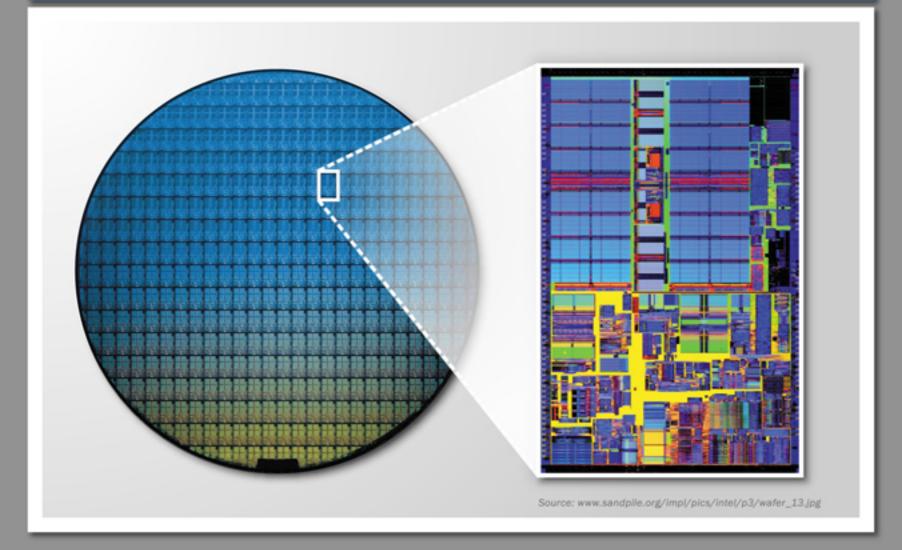

#### Each Silicon Wafer Is Capable of Yielding Hundreds of Individual Chips

'899 PATENT CDX-17

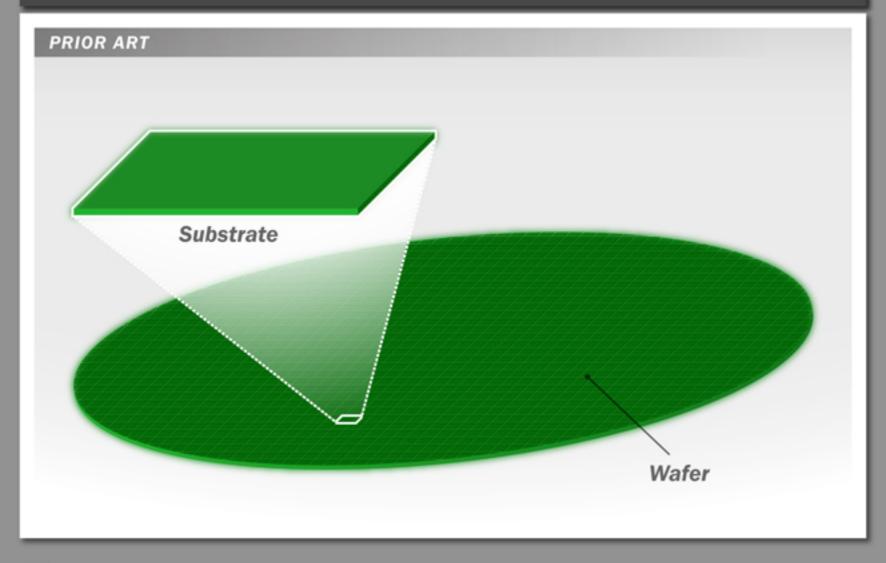

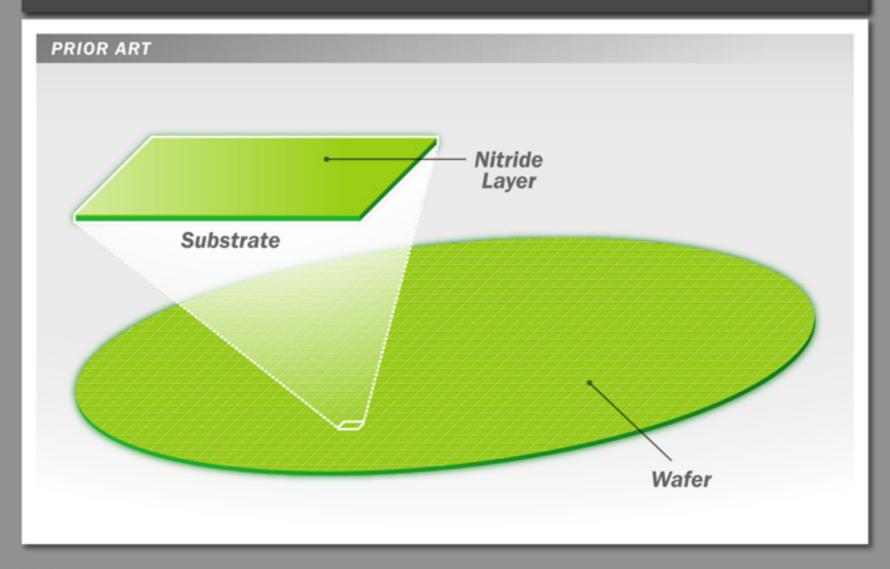

#### Semiconductor Wafer at the Beginning of a Typical STI Process

#### Nitride Is Deposited on Substrate

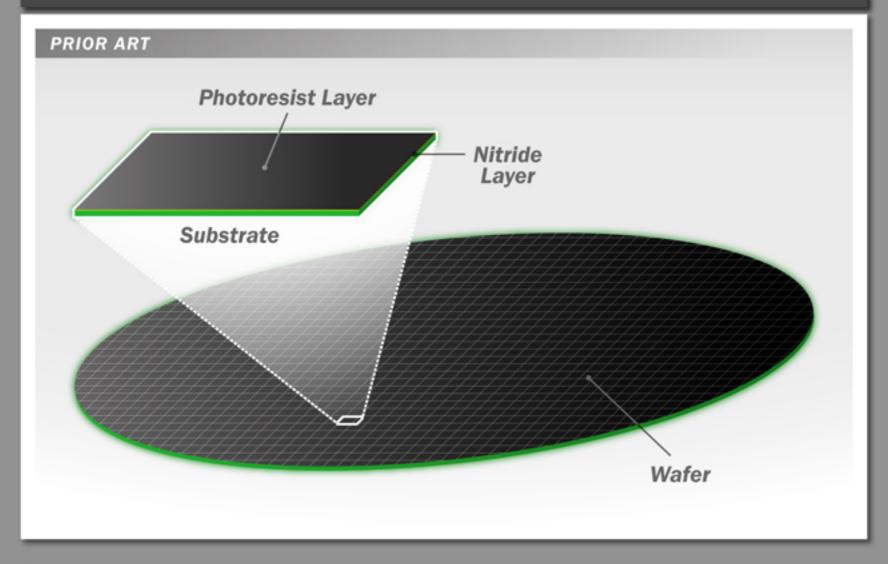

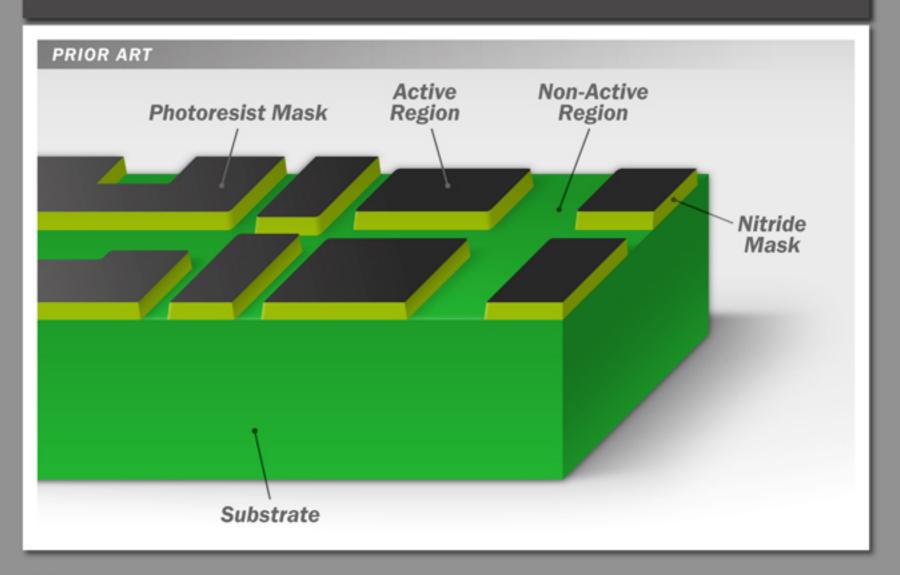

#### Photoresist Is Deposited on Top of the Nitride Layer

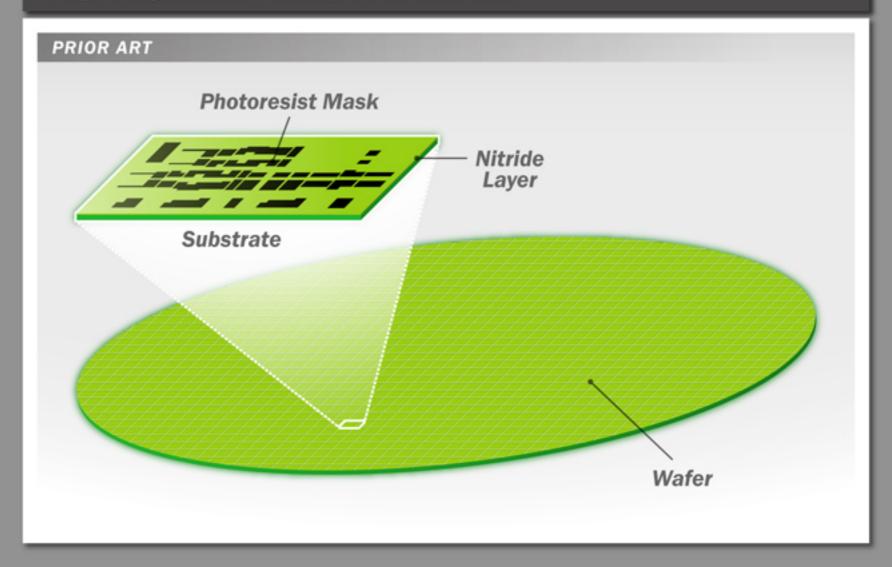

#### Photoresist Not Covered by a Mask Dissolves, Exposing the Nitride Layer Underneath

#### The Photoresist Mask Defines the Locations of Active Regions

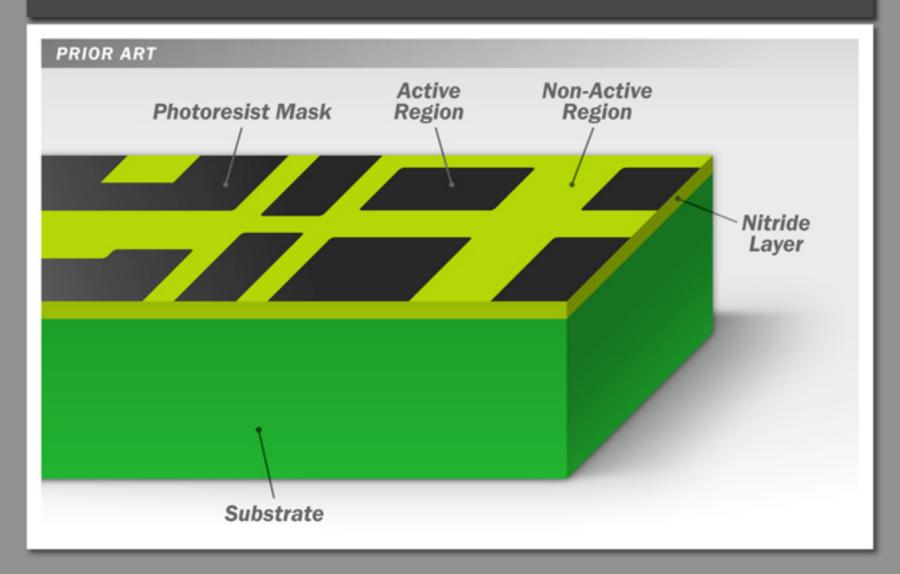

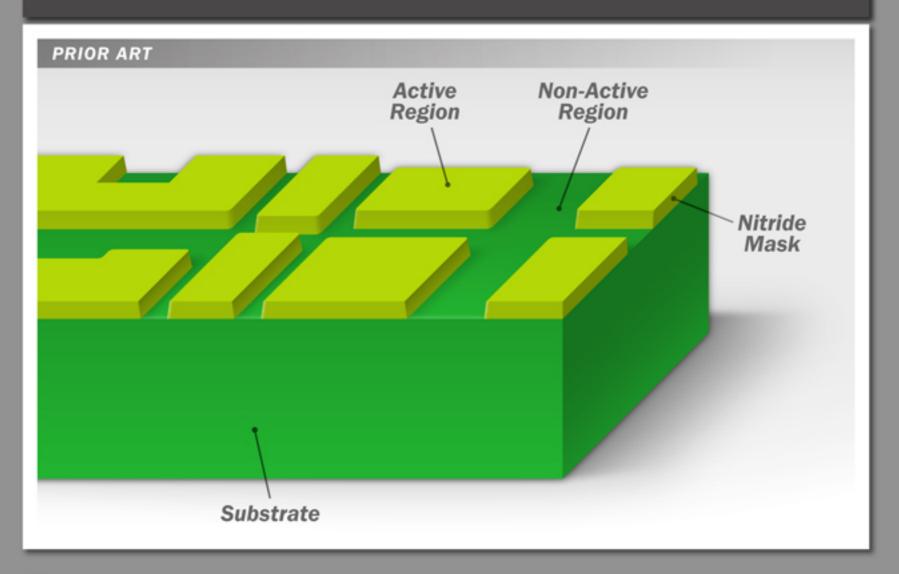

#### The Exposed Nitride in the Non-Active Regions Is Removed

#### The Remaining Nitride Layer Masks the Active Regions

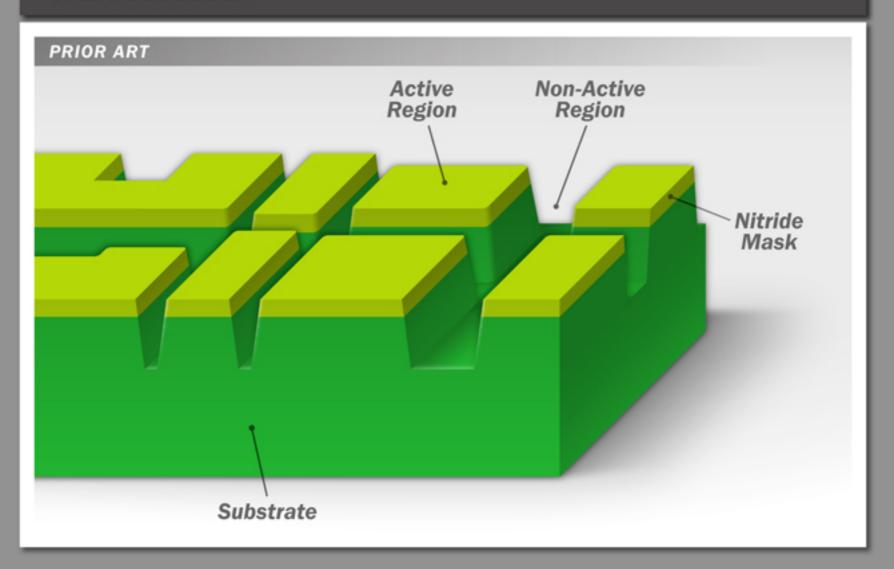

# Trenches Are Etched into the Exposed Non-Active Regions of the Substrate

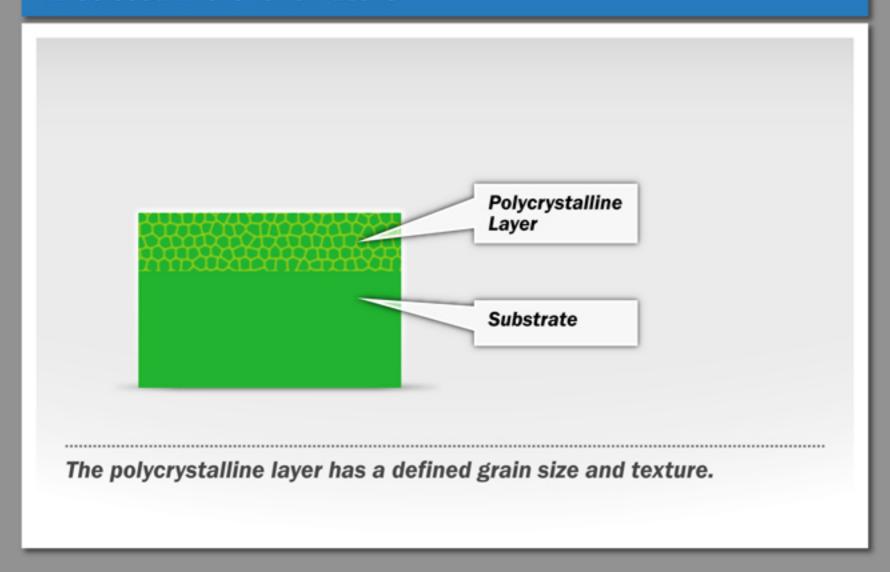

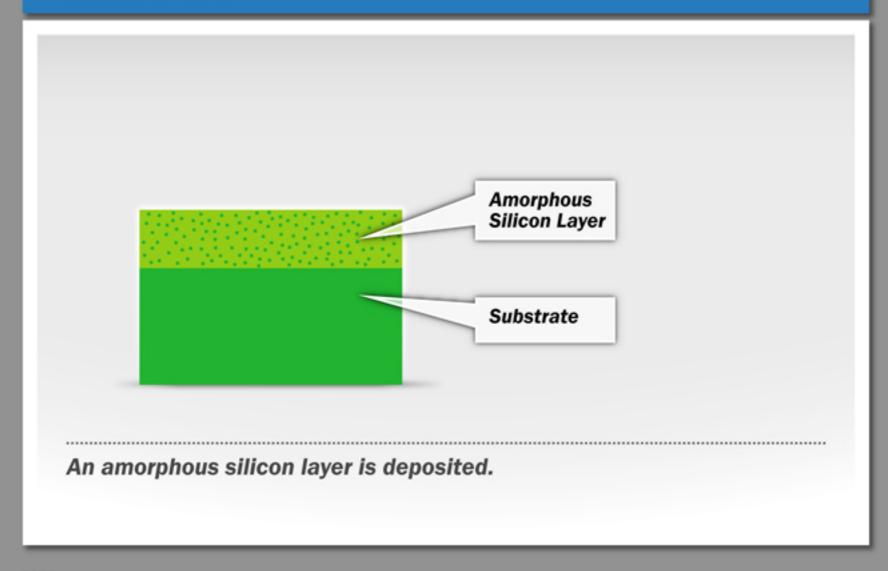

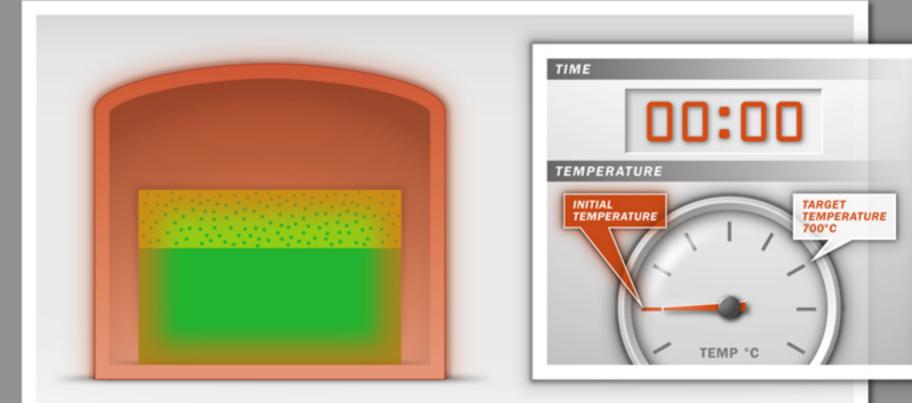

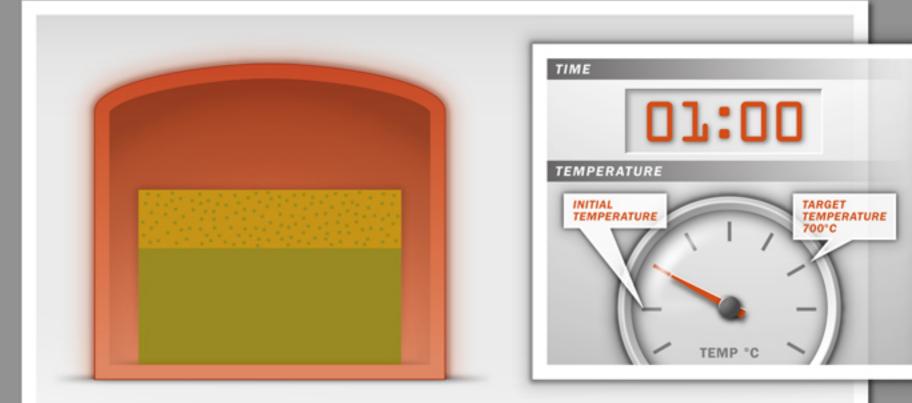

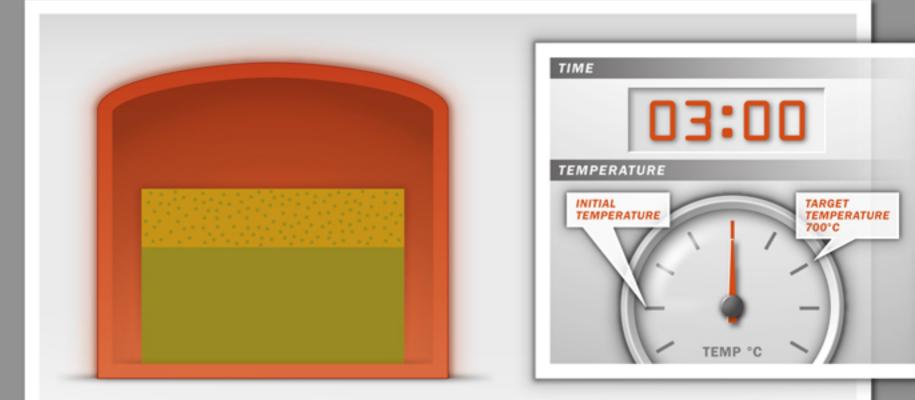

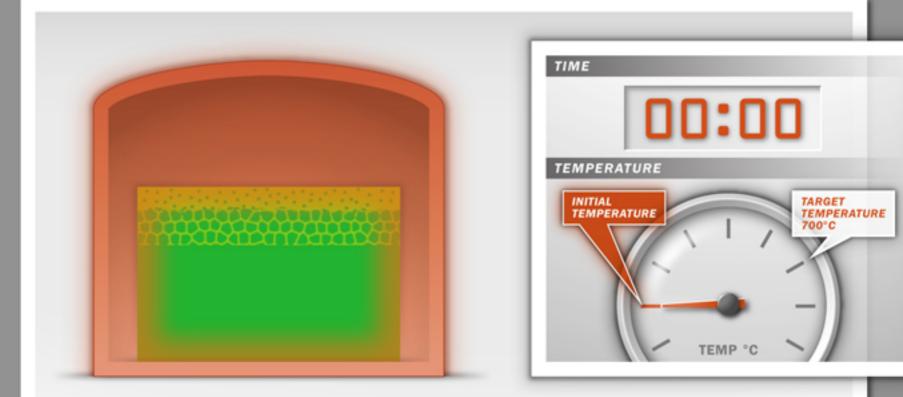

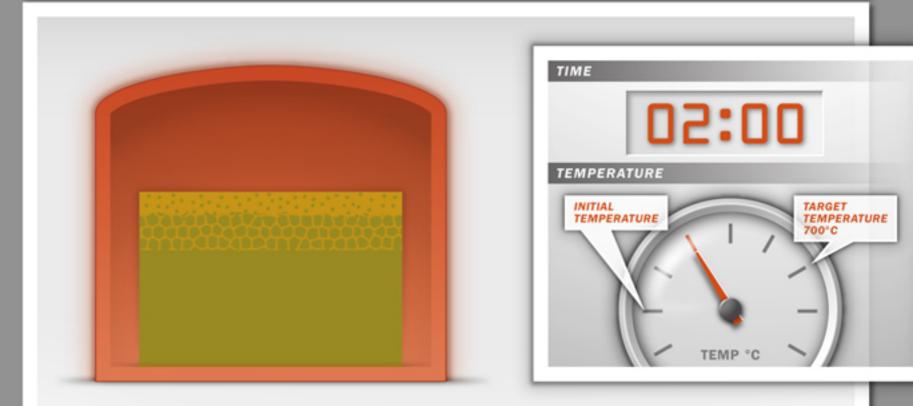

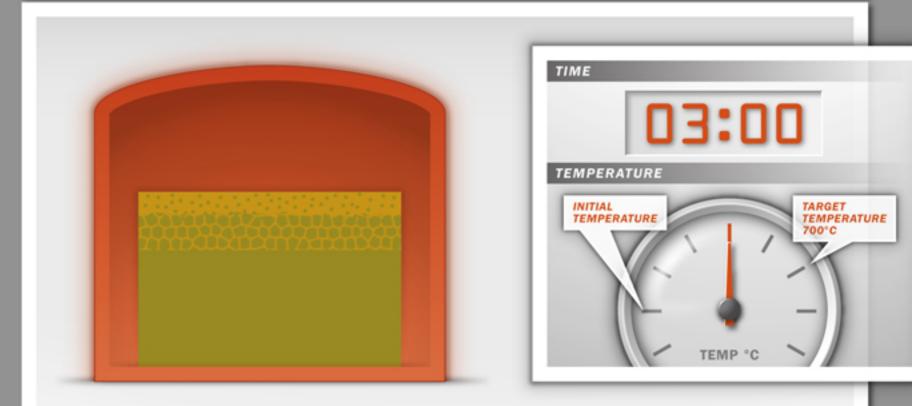

Substrate with amorphous layer is heated to an initial temperature that is LOWER than the crystallization temperature.

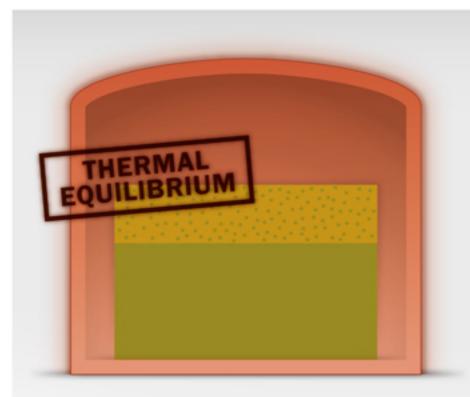

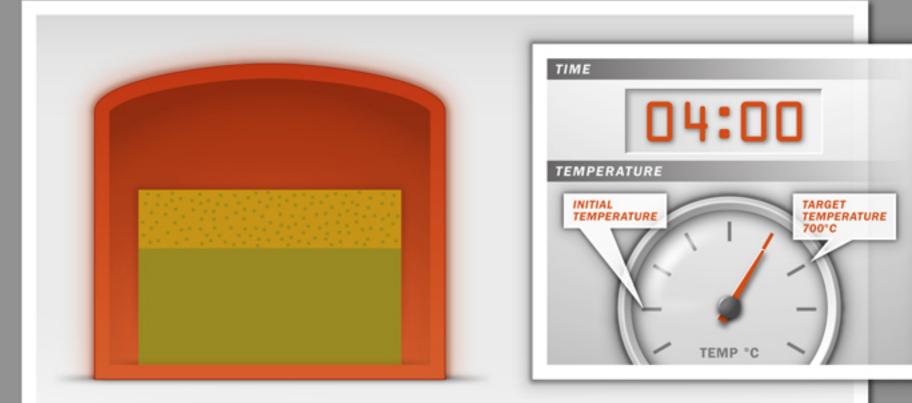

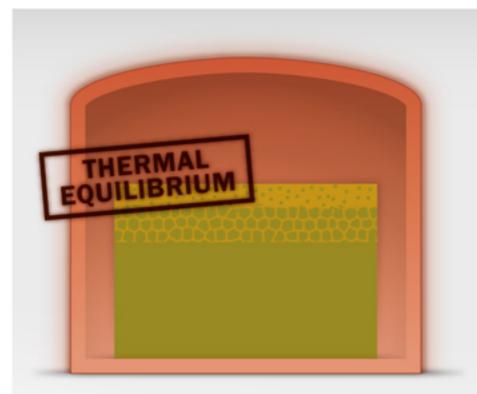

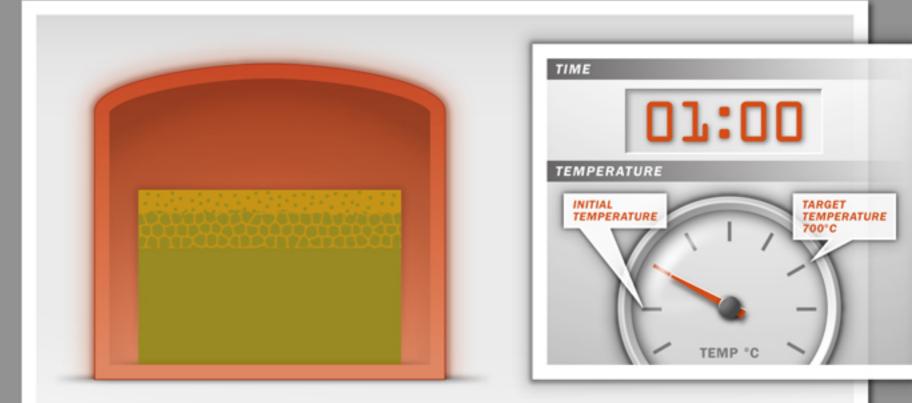

Substrate with amorphous silicon layer is held at initial temperature to achieve a thermal equilibrium.

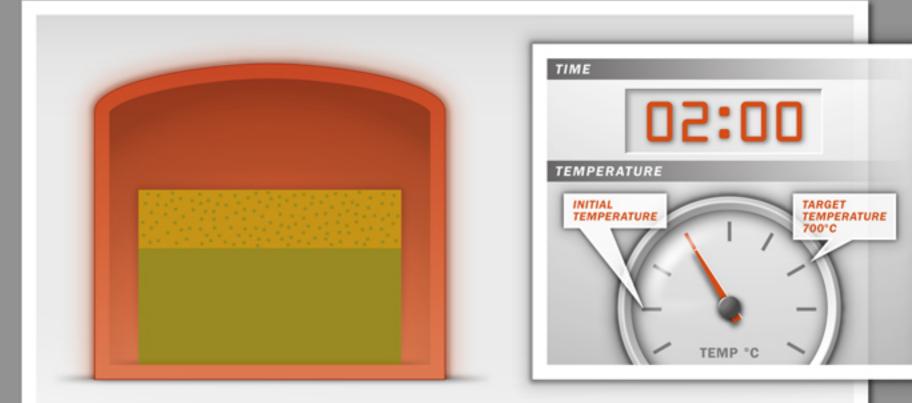

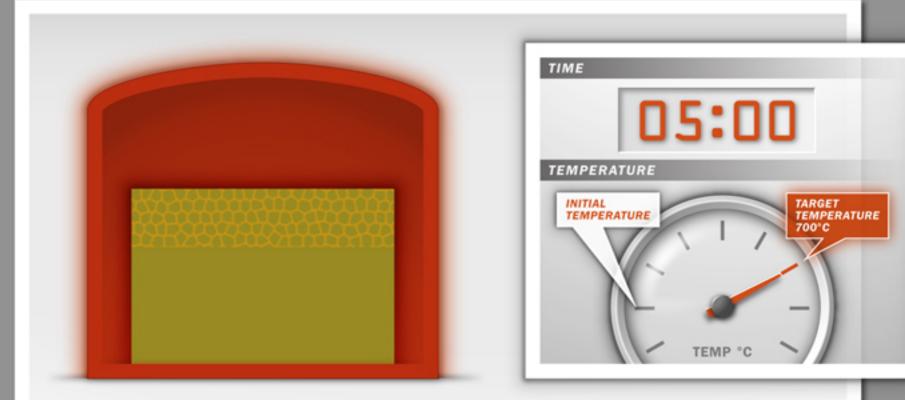

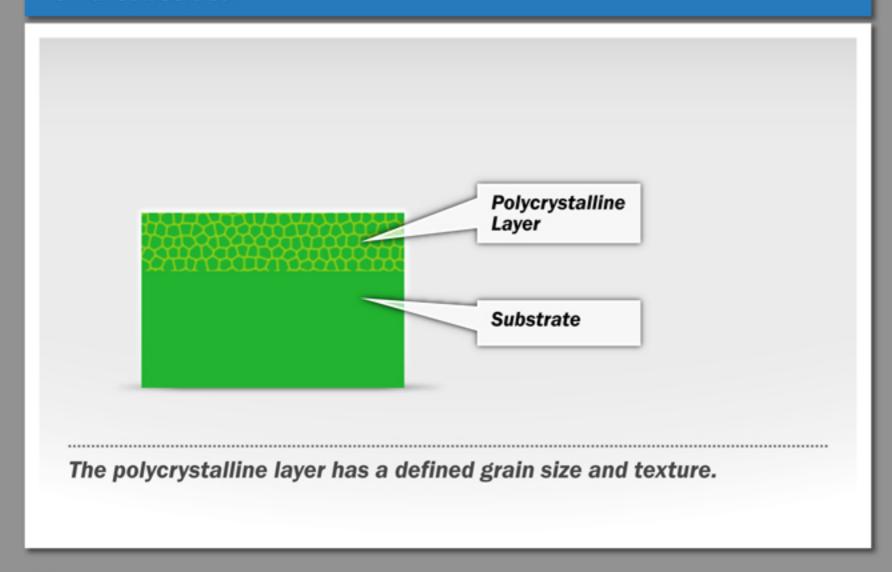

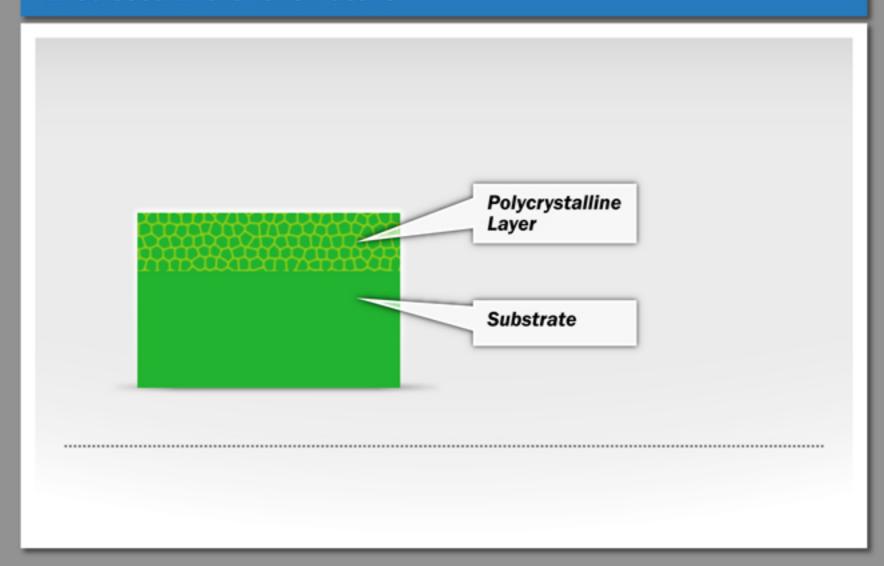

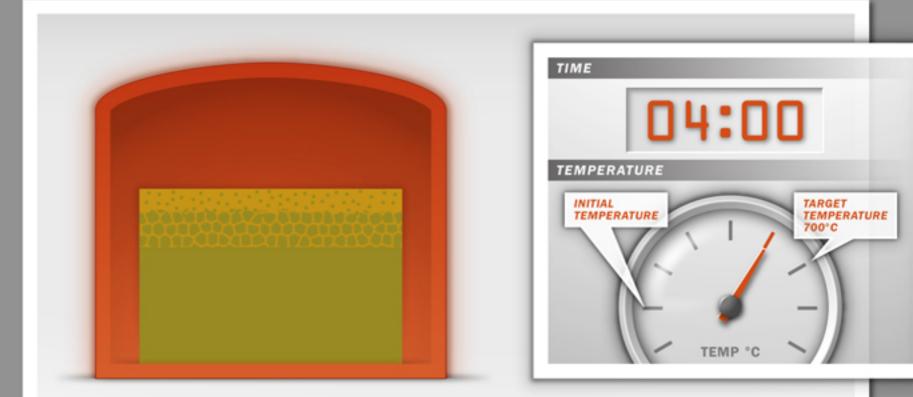

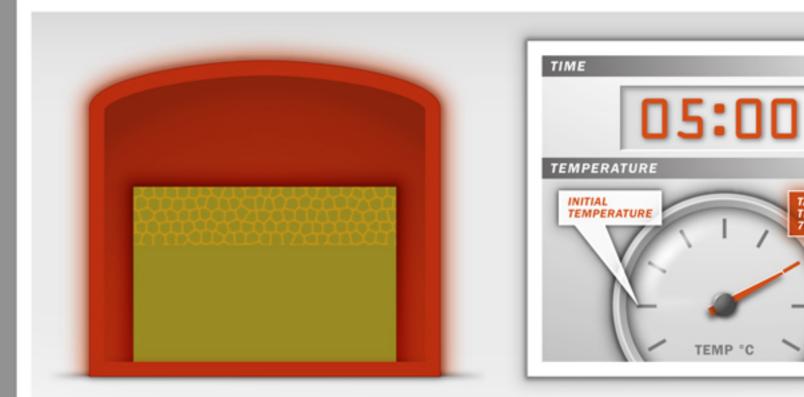

At the target temperature, the amorphous silicon layer crystallizes into the desired polycrystalline layer.

The ion implantation step damages silicon crystal structure, causing it to become amorphous.

Substrate with amorphous layer is heated to an initial temperature that is LOWER than the crystallization temperature.

Substrate with amorphous silicon layer is held at initial temperature to achieve a thermal equilibrium.

TEMPERATURE

The controlled heating causes recrystallization into a polycrystalline layer having a defined grain size and texture.